|

|

||||||||||||

|

|

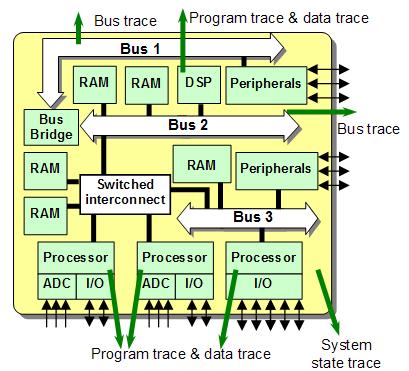

Debug support strategy for Systems-on-Chips with multiple processor cores. The continuous advancement in technology for Systems-on-Chips (SoCs) results in novel challenges for system development: previously used debug strategies for hardware and application software development have either become obsolete, unreliable or insufficient. This research investigates new efficient approaches to support hardware and application software development for embedded SoCs with multiple processor cores. This project is developing a comprehensive system centric debug support strategy for use with SoCs that have multiple processor cores and active peripherals. The strategy is designed for the requirements of hard real-time embedded systems developers with a special focus on the automotive and hard-disk drive controller sectors where calibration at run-time is required. Support is included for the development of embedded systems in all product sectors including those having real-time operating systems and products for use in low cost product areas. The primary hardware solutions centre on very low pin count debug support with an improved feature set and performance. Our scalable and highly configurable on-chip debug support strategy targets systems with one to sixteen cores but supports a greater number through the use of a hierarchical approach. This project’s solutions are compatible with current and many future system interconnects, including hierarchical busses and parallel interconnect structures and has considered ‘globally asynchronous locally synchronous’ implementation approaches from the start to provide deterministic debug support in SoC implemented in deep sub-micron integration processes. A further continuation of this project is the design and development of software debugging tools to assist with the development, debugging and calibration of both multiple processor core systems and their associated embedded software. The software tool flow is intended to fill the voids left by existing commercial and open source tools that only consider systems with either a single type of processor or expect separate debug support interfaces for each processor core. It aims to provide coherent access to the on-chip debug support resources from multiple heterogeneous processor cores by building on our generic hardware debug support strategy or through the use of interface adapters, the multiple processor core debug support strategies of other IP vendors. The software development program incorporates intelligent analysis of tool user requirements, from development features through to ease of use and straight forward user interfaces. This project has the ultimate target of increasing developer productivity leading to reduced time to market for products and a strong competitive edge for businesses using our advanced debug support strategy for systems on-chip with multiple processor cores. This project is funded by EPSRC grant GR/S13361/01. Contact: Dr. Klaus D. McDonald-Maier

This page was last modified on 08-04-04. |

| [Home] [About Me] [Research] [Debug] [Optical Processors] [Publications] [Teaching] |